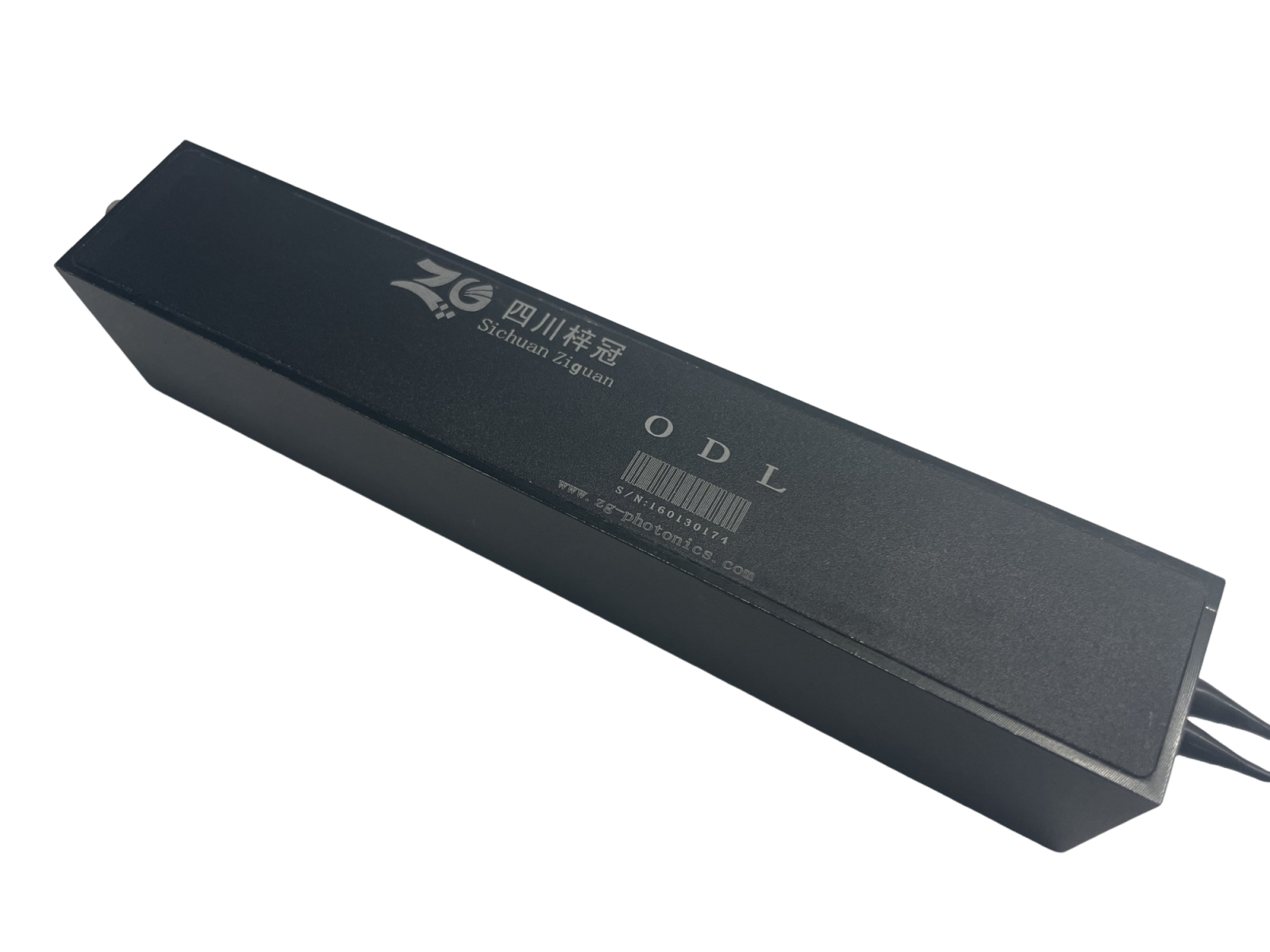

压控延迟线工作原理、结构、特点及应用全解析

在现代电子系统中,时钟信号的精确同步与控制是确保系统稳定运行的核心。压控延迟线(Voltage-Controlled Delay Line,VCDL)作为一种通过电压调节信号延迟时间的电路模块,已成为高速通信、雷达探测、芯片测试等领域的核心技术。四川梓冠光电将从工作原理、结构特点、应用场景及用户痛点四个维度,全面解析压控延迟线的技术内涵。

一、压控延迟线的工作原理:电压驱动的延迟调控

压控延迟线基于“电压-延迟”线性映射机制,通过调节控制电压改变信号传播路径的延迟时间。其核心结构由多级延迟单元串联组成,每个单元包含可变电容或电流源,控制电压的变化会改变电容充放电速率或电流强度,从而直接调节信号通过时间。例如,在CMOS工艺中,通过调整PMOS电流源的栅极电压,可控制反相器翻转速度,实现亚皮秒级延迟精度。

二、压控延迟线的结构:从单元到系统的设计逻辑

压控延迟线的典型结构包含四个层级:

1、延迟单元:核心模块,分为差分型与单端型。差分结构采用源极耦合对管,通过尾电流源控制延迟,具有强共模噪声抑制能力;单端结构基于反向器改进,如电流饥饿型延迟单元,通过调节负载电阻实现延迟控制。

2、级联拓扑:多级延迟单元串联形成延迟链,通过级数调节总延迟范围。例如,4级延迟链可实现360°相位覆盖,满足时钟同步需求。

3、控制接口:包括电荷泵锁相环(CP-PLL)或鉴频鉴相器(PFD),用于生成与参考时钟同步的控制电压。

4、输出缓冲:通过反相器链将延迟信号整形为标准逻辑电平,确保信号完整性。

三、压控延迟线的特点:性能与设计的权衡

1、高精度:在先进工艺下,单级延迟单元可实现<50fs的分辨率,满足高速串行接口(如PCIe 6.0)的抖动要求。

2、线性度:通过优化负载匹配与电流源设计,可实现>95%的电压-延迟线性度,降低系统误差。

3、抖动抑制:采用差分结构与片内稳压电源,可将电源噪声引起的抖动控制在<10ps以内。

4、面积与功耗:差分结构需双倍晶体管资源,功耗较单端结构高20%-30%,需根据应用场景权衡。

四、压控延迟线的应用:从实验室到工业场景

1、高速通信:在100G-400G光模块中,VCDL用于时钟数据恢复(CDR),通过精确相位对齐实现误码率<10^-15。

2、雷达系统:在相控阵雷达中,VCDL作为时延补偿模块,通过动态调节延迟时间实现波束指向的毫秒级切换。

3、芯片测试:在ATE设备中,VCDL用于产生多相位时钟,支持并行测试效率提升50%以上。

4、光通信:在光纤延迟线中,VCDL结合声光调制器,实现纳秒级延迟调节,用于光信号处理。

五、用户关心的问题及解决办法

1、如何选择合适的压控延迟线?

用户在选择压控延迟线时,应综合考虑其工作频率范围、延迟时间范围、线性度、稳定性以及成本等因素。同时,还应根据具体应用场景的需求,选择合适的封装形式和接口类型。

2、如何解决压控延迟线的非线性问题?

压控延迟线在实际应用中可能会遇到非线性问题,即延迟时间与控制电压之间不是完全的线性关系。为了解决这一问题,可以采用预失真技术或反馈控制技术等手段进行补偿和校正。

3、如何降低压控延迟线的噪声和干扰?

压控延迟线在工作过程中可能会受到外界噪声和干扰的影响,从而影响其性能表现。为了降低噪声和干扰的影响,可以采用屏蔽技术、滤波技术或接地技术等手段进行防护和隔离。

结语

压控延迟线作为电子系统中的“时间雕刻师”,其技术演进正推动着通信速率、雷达精度与测试效率的极限突破。随着3D集成、硅光子等技术的融合,VCDL有望在量子计算、6G通信等前沿领域发挥更大价值。对于工程师而言,深入理解其工作原理与设计方法,是攻克下一代电子系统时序挑战的关键。